## UNIVERSIDADE FEDERAL DO PARÁ INSTITUTO DE TECNOLOGIA PROGRAMA DE PÓS-GRADUÇÃO EM ENGENHARIA ELÉTRICA

| FPGA-Based Testbed for Fronthaul Signal Compression: Implementation and Validation |

|------------------------------------------------------------------------------------|

| Joary Paulo Wanzeler Fortuna                                                       |

|                                                                                    |

| <b>DM</b> : 16/2017                                                                |

UFPA / ITEC / PPGEE

Campus Universitário do Guamá

Belém-Pará-Brasil

2016

# UNIVERSIDADE FEDERAL DO PARÁ INSTITUTO DE TECNOLOGIA PROGRAMA DE PÓS-GRADUÇÃO EM ENGENHARIA ELÉTRICA

| Joary Paulo Wanzeler Fortuna                                                      |   |

|-----------------------------------------------------------------------------------|---|

| FPGA-Based Testbed for Fronthaul Signal Compression: Implementation and Validatio | n |

| <b>DM</b> : 16/2017                                                               |   |

UFPA / ITEC / PPGEE

Campus Universitário do Guamá

Belém-Pará-Brasil

2016

# UNIVERSIDADE FEDERAL DO PARÁ INSTITUTO DE TECNOLOGIA PROGRAMA DE PÓS-GRADUÇÃO EM ENGENHARIA ELÉTRICA

| Inary   | Paulo  | Wanzeler  | Fortung   |

|---------|--------|-----------|-----------|

| .ivai v | i auiv | Wallzeiei | T'UI tuna |

FPGA-Based Testbed for Fronthaul Signal Compression: Implementation and Validation

A dissertation submitted to the examination committee in the graduate department of Electrical Engineering at the Federal University of Pará in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering with emphasis in Telecommunications.

UFPA / ITEC / PPGEE

Campus Universitário do Guamá

Belém-Pará-Brasil

2016

#### FPGA-Based Testbed for Fronthaul Signal Compression: Implementation and Validation

| Dissertação de mestrado subr        | metida à avaliação da banca examinadora aprovada pelo   |

|-------------------------------------|---------------------------------------------------------|

| colegiado do Programa de Pós-Grad   | uação em Engenharia Elétrica da Universidade Federal do |

| Pará e julgada adequada para obtenç | ção do Grau de Mestre em Engenharia Elétrica na área de |

| Telecomunicações.                   |                                                         |

| ·                                   |                                                         |

|                                     |                                                         |

| Aprovada em///                      |                                                         |

|                                     |                                                         |

|                                     |                                                         |

|                                     |                                                         |

|                                     |                                                         |

|                                     |                                                         |

| _                                   | Aldebaro Barreto da Rocha Klautau Júnior                |

|                                     | ADVISER                                                 |

|                                     |                                                         |

|                                     |                                                         |

|                                     |                                                         |

| _                                   | Leonardo Lira Ramalho                                   |

|                                     | CO-ADVISER                                              |

|                                     |                                                         |

|                                     |                                                         |

|                                     |                                                         |

| _                                   | João Crisóstomo Weyl Albuquerque Costa                  |

|                                     | MEMBER OF EXAMINATION COMISSION                         |

|                                     |                                                         |

|                                     |                                                         |

|                                     |                                                         |

| _                                   | Daniel Cardoso de Souza                                 |

MEMBER OF EXAMINATION COMISSION

| _     | Roberto Menezes Rodrigues                  |

|-------|--------------------------------------------|

|       | MEMBER OF EXAMINATION COMISSION            |

|       |                                            |

| _     |                                            |

|       | Evaldo Gonçalves Pelaes                    |

| DIRET | OR DA PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA |

## Acknowledgments

The author would like to thanks firstly God for helping in the difficult moments. Then, his family for support and patience. Also, to his advisor and co-adivisor for all the hard work invested in this dissertation. Finally, thank to all the work team of LASSE for all the acquired experience.

Joary Paulo Wanzeler Fortuna

March 2017

"They did not know it was impossible so they did it"

## Acronyms

ADC Analog to Digital Converter

AWG Arbitrary Waveform Generator

AXI Advanced Extensible Interface

BBU Base Band Unit

BER Bit Error Rate

BF Basic Frame

BRAM Block Random Access Memory

BS Base Station

BW Bandwidth

CAPEX Capital Expenditures

CDMA Code Division Multiple Access

CM Configuration Management

CP Cyclic Prefix

CPRI Common Public Radio Interface

CPU Central Processing Unit

C-RS Cell-Specific Reference Signal

CW Control Word

DAC Digital to Analog Converter

DASH Dynamic Adaptive Streaming over HTTP

DDR Double Data Rate

DFT Discrete Fourier Transform

DFTS Discrete Fourier Transform-Spread

DHCP Dynamic Host Configuration Protocol

DMA Direct Memory Access

DU Digital Unit

EDGE Enhanced Data Rates for GSM Evolution

EVM Error Vector Magnitude

FFT Fast Fourier Transform

FIFO First In First Out

FIR Finite Impulse Response

FPGA Field Programmable Gate Array

FSM Finite State Machine

FTP File Transfer Protocol

GNSS Global Navigation Satellite System

GPS Global Positioning System

GSM Global System for Mobile Communications

HARQ Hybrid Automatic Repeat Request

HDLC High-Level Data Link Control

IEEE Institute of Electrical and Electronics Engineers

IFFT Inverse Fast Fourier Transform

IP Internet Protocol

LPC Linear Predictive Coding

ISG Industry Specification Group

ITU International Telecommunications Union

JTAG Joint Test Action Group

LSB Least Significant Bit

LTE Long Term Evolution

LUT Lookup table

MAC Media Access Control Layer

MIMO Multiple Input Multiple Output

MMCM Mixed-Mode Clock Manager

MSB Most Significant Bit

NGFI Next Generation Fronthaul Interface

NQ Non-Quantized

OAM Operation and Maintenance

OBSAI Open Base Station Architecture Initiative

OFDM Orthogonal Frequency-Division Multiplexing

OPEX Operation Expenditures

ORI Open Radio Equipment Interface

PBCH Physical Broadcast Channel

PCFICH Physical Control Format Indicator Channel

PDCCH Physical Downlink Control Channel

PDSCH Physical Downlink Shared Channel

PDV Packet Delay Variation

PHICH Physical Hybrid-ARQ Indicator Channel

PHY Physical Layer

PLL Phase Locked Loop

PTP Precision Time Protocol

PUSQH Predictive Uniform Scalar Quantization with Huffman

QAM Quadrature Amplitude Modulation

RAN Radio Access Network

RAT Radio Access Technology

RB Resource Block

RE Resource Element

REC Radio Equipment Controller

RF Radio Frequency

RRU Remote Radio Unit

RTC Real-Time Clock

RTT Round Trip Time

RU Radio Unit

SMA SubMiniature Version-A Cable

TCP Transmission Control Protocol

TOC Total Ownership Cost

TSN Time Sensitive Network

UART Universal Asynchronous Receiver/Transmitter

UFPA Federal University of Pará

UMTS Universal Mobile Telecommunications Service

VHDL VHSIC Hardware Description Language

VSA Vector Signal Analyzer

WCDMA Wideband Code Division Multiple Access

WDM Wavelength-Division Multiplexing

WIMAX Worldwide Interoperability for Microwave Access

## **Symbols**

$\hat{d}$

One way delay estimation by PTP

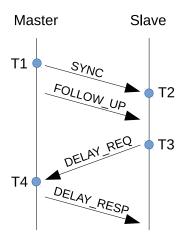

$N_{AxC}$ Number of antennas carried over the Fronthaul  $IQ_b$ Number of bits per complex IQ sample  $F_{s}$ Sample rate of the LTE signal transported over the Fronthaul  $R_{CPRI}$ CPRI bit-rate used on the Fronthaul configuration  $N_R$ CPRI line-rate option used on the Fronthaul configuration OVOverhead generated by the Ethernet header and fronthaul Metadata on the CPRI stream  $H_s$ Number of bits allocated for the headers on each Ethernet frame  $N_{BF}$ Number of CPRI Basic Frames transported on each Ethernet frame JMaximum accumulation jitter created by Basic Frame accumulation  $T_{1.k}$ Timestamp acquired by PTP at the transmission of SYNC message Timestamp acquired by PTP at the reception of SYNC message  $T_{2.k}$  $T_{3,k}$ Timestamp acquired by PTP at the transmission of DELAY\_REQ message  $T_{4.k}$ Timestamp acquired by PTP at the reception of DELAY\_REQ message Calculated frequency offset error by PTP yCalculated time offset error by PTP x $T_{sm}$ One way delay from PTP slave to master  $T_{ms}$ One way delay from PTP master to slave

## **List of Figures**

| 2.1  | The fronthaul evolution.                                                        | 5  |

|------|---------------------------------------------------------------------------------|----|

| 2.2  | Information carried in CPRI link                                                | 8  |

| 2.3  | CPRI Basic Frame internal structure [1]                                         | 10 |

| 2.4  | Example of CPRI Basic Frame carrying two signals with 30 bits per IQ sample.    | 10 |

| 2.5  | CPRI naming convention and frame structure [1]                                  | 11 |

| 2.6  | Overview of OBSAI building blocks [2]                                           | 12 |

| 2.7  | Information carried by OBSAI RP3 link                                           | 13 |

| 2.8  | CPRI and ORI control sub-channels mapping                                       | 15 |

| 2.9  | LTE base station possible functional splits: (a) All process centralized in the |    |

|      | BBU, (b) The OFDM modulation is executed in RRU, (c) The resource mapping       |    |

|      | and modulation is executed in RRU, (d) The whole PHY layer is executed in       |    |

|      | RRU, (e) All functions except the PDCP is executed in the RRU                   | 19 |

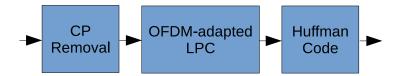

| 2.10 | PUSQH compression flow graph                                                    | 23 |

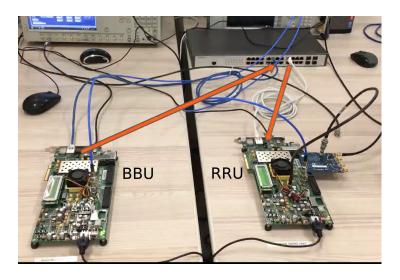

| 3.1  | Hardware setup of the testbed FPGA boards                                       | 26 |

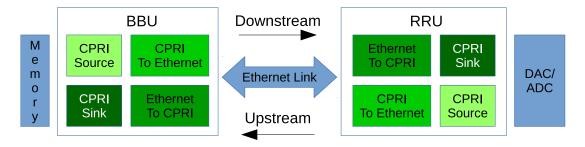

| 3.2  | Fronthaul testbed architecture                                                  | 26 |

| 3.3  | Default CPRI Basic Frame configuration                                          | 29 |

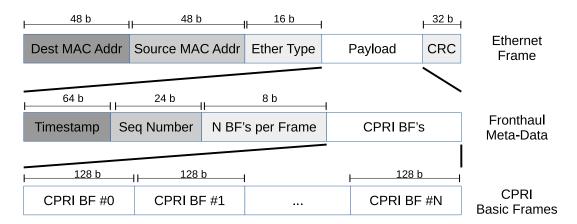

| 3.4  | Example of CPRI encapsulation on Ethernet frame                                 | 30 |

| 3.5  | PTP messages and timestamps                                                     | 32 |

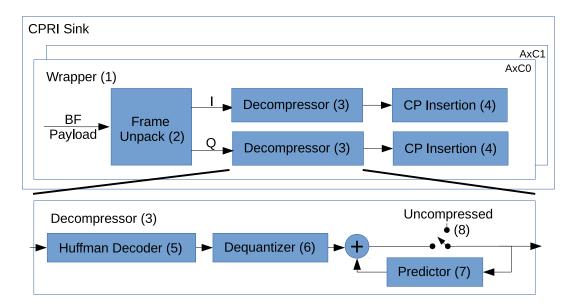

| 3.6  | Decompressor blocks flow graph                                                  | 35 |

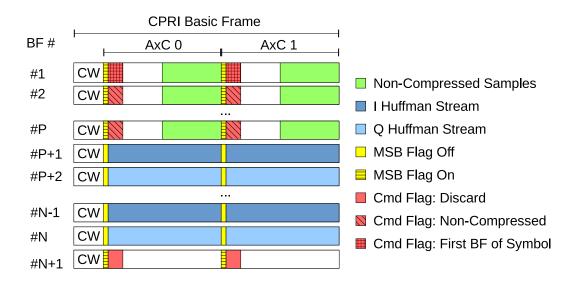

| 3.7  | CPRI BF payload for the bit-stream of compressed OFDM symbol                    | 37 |

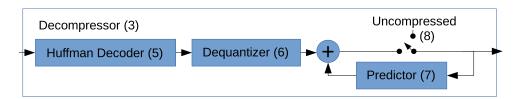

| 3.8  | Decompressor with its internal blocks: Huffman and LPC decoders                 | 38 |

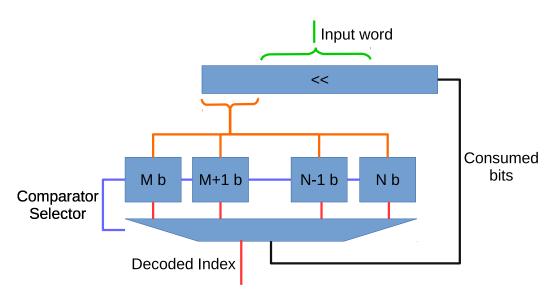

| 3.9  | Huffman decoder internal flow graph                                             | 40 |

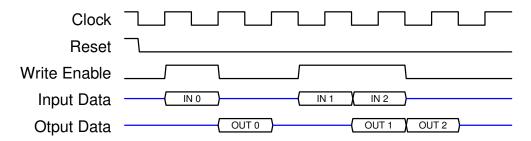

| 3.10 | Timing overview of prediction filter input and output signals                   | 42 |

| 3.11 | Fixed point Q-format of internal signals on prediction filter                   | 42 |

|      |                                                                               | xiii                                                                                                                                                                                                                                                                                                                                                                             |

|------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

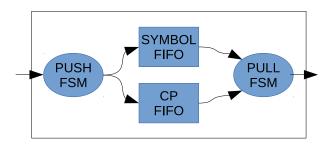

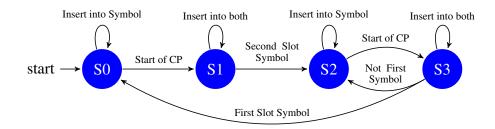

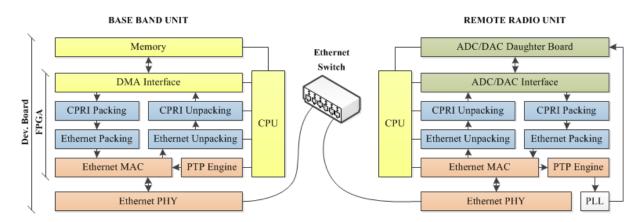

| 3.12 | Machines and FIFOs used in CP insertion block                                 | 44                                                                                                                                                                                                                                                                                                                                                                               |

| 3.13 | Overview of the cyclic prefix insertion block state machines                  | 45                                                                                                                                                                                                                                                                                                                                                                               |

| 4.1  | Fronthaul testbed blocks                                                      | 46                                                                                                                                                                                                                                                                                                                                                                               |

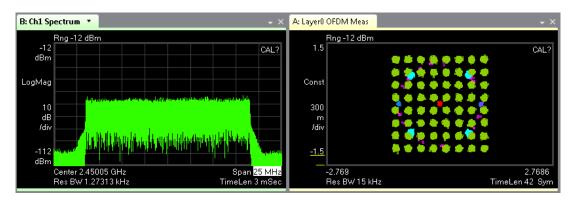

| 4.2  | RF LTE signal, after fronthaul transport and decompression. The left graph is |                                                                                                                                                                                                                                                                                                                                                                                  |

|      | the spectrum of the signal, centred in 2.45 GHz. The right graph shows the    |                                                                                                                                                                                                                                                                                                                                                                                  |

|      | constellation of the decoded physical channels used in LTE                    | 49                                                                                                                                                                                                                                                                                                                                                                               |

| 4.3  | Clock and data path on the RRU                                                | 50                                                                                                                                                                                                                                                                                                                                                                               |

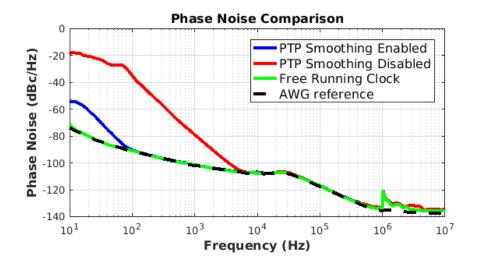

| 4.4  | Phase Noise comparison between PTP, free-running clock and AWG reference.     | 51                                                                                                                                                                                                                                                                                                                                                                               |

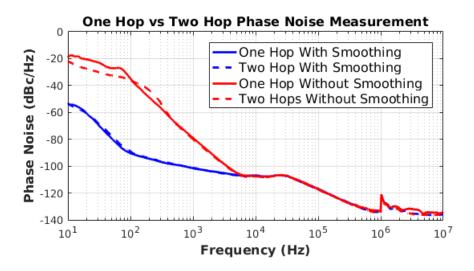

| 4.5  | One Hop vs Two Hops Phase Noise measurement                                   | 52                                                                                                                                                                                                                                                                                                                                                                               |

|      | <ul><li>3.13</li><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul>        | <ul> <li>4.2 RF LTE signal, after fronthaul transport and decompression. The left graph is the spectrum of the signal, centred in 2.45 GHz. The right graph shows the constellation of the decoded physical channels used in LTE.</li> <li>4.3 Clock and data path on the RRU.</li> <li>4.4 Phase Noise comparison between PTP, free-running clock and AWG reference.</li> </ul> |

## **List of Tables**

| 2.1 | CPRI configuration for some of the line rates defined in the specification | 9  |

|-----|----------------------------------------------------------------------------|----|

| 2.2 | Fronthaul requirements of different functional split from [3]              | 19 |

| 3.1 | Default parameters of fronthaul's transported signal used in this work     | 29 |

| 3.2 | List of Flags incorporated on the compressed stream                        | 36 |

| 3.3 | Number of samples and duration per Symbol OFDM in an LTE slot. The length  |    |

|     | of CP is different for the first OFDM symbol                               | 43 |

| 4.1 | Hardware Utilization for BBU and RRU                                       | 48 |

| 4.2 | EVM measurements break down of the different LTE channels [4]              | 49 |

| 43  | Ethernet link usage break down                                             | 50 |

## **Contents**

| A  | cknow          | vledgme       | ent                                               | V   |  |  |

|----|----------------|---------------|---------------------------------------------------|-----|--|--|

| Li | ist of Figures |               |                                                   |     |  |  |

| Li | st of T        | <b>Fables</b> |                                                   | xiv |  |  |

| Co | ontent         | ts            |                                                   | xv  |  |  |

| 1  | Intr           | oductio       | n and Motivation                                  | 1   |  |  |

|    | 1.1            | Object        | tives                                             | 3   |  |  |

|    | 1.2            | Disser        | tation Outline                                    | 3   |  |  |

| 2  | Froi           | onthaul       |                                                   |     |  |  |

|    | 2.1            | Fronth        | aul Concepts and Existing Technologies            | 7   |  |  |

|    |                | 2.1.1         | Common Public Radio Interface (CPRI)              | 8   |  |  |

|    |                | 2.1.2         | Open Base Station Architecture Initiative (OBSAI) | 12  |  |  |

|    |                | 2.1.3         | Open Radio Equipment Interface (ORI)              | 14  |  |  |

|    | 2.2            | Next C        | Generation Fronthaul Interface (NGFI)             | 15  |  |  |

|    |                | 2.2.1         | Packet-Based Fronthaul                            | 17  |  |  |

|    |                | 2.2.2         | Functional Split between BBU and RRU              | 18  |  |  |

|    | 2.3            | Fronth        | naul's Signal Compression                         | 22  |  |  |

|    |                | 2.3.1         | PUSQH Compression Algorithm                       | 22  |  |  |

| 3  | Froi           | nthaul I      | Ethernet Compression Testbed                      | 25  |  |  |

|    | 3.1            | Ethern        | net Fronthaul Testbed                             | 26  |  |  |

|    |                | 3.1.1         | CPRI Generation and Consuming                     | 27  |  |  |

|    |                | 3.1.2         | Encapsulation of CPRI into Ethernet               | 29  |  |  |

|    |        |         |                                    | xvi |

|----|--------|---------|------------------------------------|-----|

|    |        | 3.1.3   | Clock Synchronization Procedures   | 32  |

|    | 3.2    | Fronth  | aul Compression Implementation     | 34  |

|    |        | 3.2.1   | Unpacking CPRI Basic Frames        | 36  |

|    |        | 3.2.2   | Decompressor Implementation        | 38  |

|    |        | 3.2.3   | Huffman Decoder Block              | 39  |

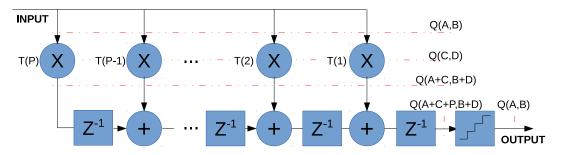

|    |        | 3.2.4   | Prediction Filter Block            | 41  |

|    |        | 3.2.5   | Cyclic Prefix Insertion Block      | 43  |

| 4  | Test   | bed Eva | aluation Results                   | 46  |

|    | 4.1    | Testbe  | d evaluation                       | 46  |

|    |        | 4.1.1   | Compression Evaluation             | 48  |

|    |        | 4.1.2   | The Phase Noise of recovered clock | 50  |

| 5  | Con    | clusion |                                    | 53  |

|    | 5.1    | Future  | Works                              | 54  |

|    | 5.2    | Publica | ation                              | 55  |

| Bi | bliogi | raphy   |                                    | 56  |

#### **Abstract**

In recent years the world has seen an increasing demand for mobile services with high capacity and low cost. Such requirements forced the radio access technologies to be rethought. Among the different architectures proposed in literature, one that has got a lot of attention was the Centralized Radio Access Network (C-RAN). This strategy proposes to share the network resources through the centralization of the base-band processing and, as a result, reduce the network cost. Even though the centralization can bring several benefits, it also increases the distance between the point where the signal is captured and the point where it is processed. The link connecting both points is called fronthaul. In this scenario, the existing fronthaul technologies do not fit in the flexibility and cost requisites expected for the next generation mobile network, mainly due to the usage of dedicated optical links. One solution to these problems is the usage of Ethernet to transport fronthaul data, due to its ubiquitous presence, flexibility and low cost. In this work, a testbed for fronthaul based on Ethernet is presented, along with the implementation details and validation results. Also motivated by the Ethernet's bandwidth limitation, this work presents the VHDL implementation of a compression technique for LTE signals, evaluated in real transport conditions with the testbed. The obtained results indicate that it is possible to utilize the Ethernet network infrastructure for fronthaul transport. Although, it is necessary to reduce the requirements of Fronthaul stream through, for example, the application of signal compression techniques and synchronization methods.

#### Resumo

Nos últimos anos o mundo tem visto uma demanda crescente por serviços móveis de alta capacidade e baixo custo, isto tem forçado as tecnologias da rede de acesso móvel a serem repensadas. Entre as diferentes arquiteturas propostas na literatura, uma que ganhou bastente atenção é a centralização dos recursos da rede. Essa estratégia propõe compartilhar os recursos da rede através da centralização do processamento em banda-base, e como resultado reduzir o custo da rede. Apesar da centralização trazer vários benefícios, ela também aumenta a distancia entre o ponto onde os sinais são capiturados e o ponto onde são processados, o link que conecta esses dois pontos é chamado de fronthaul. Nesse cenário, as tecnologias de fronthaul existentes não são apropriadas para os requisitos de flexibilidade e custo esperados para a próxima geração de redes fronthaul, devido principalmente ao uso de links óticos dedicados. Uma solução para esses problemas é a utilização de Ethernet para transportar o trafego fronthaul, devido à sua onipresença, flexibilidade e baixo custo. Neste trabalho um testbed para fronthaul baseado em Ethernet é apresentado, juntamente com os detalhes de implementação e resultados de validação. Além disso, motivado pela limitação em banda existente no Ethernet, este trabalho apresenta a implementação em VHDL de um algorítmo de compressão de sinais LTE, avaliado em uma rede Ethernet real através do testbed. Os resultados obtidos indicam que é possivel utilizar a infraestrutura provida pela rede Ethernet no transporte de fronthaul. Por outro lado é necessário reduzir os requisitos exigidos pelo tráfego fronthaul. Através, por exemplo, da aplicação da compressão de sinais e de técnicas de sincronismo.

## Chapter 1

### **Introduction and Motivation**

One of the essential differences between mankind and other animals is the capability to communicate. From the Egypt's pictograms to the Internet, several techniques have been used to extend the human communication through the time and space. The Electrical Engineering field, in particular, has made several contributions to the communication systems. For example, the telegraph in early 1800's, the telephone in mid 1800's and the radio in late 1800's. But only in the late 1900's the mobile communication started to take the shape known nowadays, moved by the objective to communicate everywhere with everyone.

The first mobile transceivers were simple full-duplex analog radios, but soon became necessary to control the access to radio frequency resources. Then, a more complex network was created with the necessary control mechanism and analog voice transmission, called first generation mobile network (1G). Concurrently, the advances on voice coding and encryption made possible to transport voice over a digital network, which was applied in the second generation mobile network (2G). Also, this generation introduced beneffits such as voice encryption and data services, for example the SMS and MMS.

The evolution in capacity and coverage of the mobile networks was incremental, and the generations started to be defined by a set of prerequisites. For example, the IMT-2000 [5] and IMT-Advanced [6] defined the characteristics necessary for the 3rd and 4th generations, respectively. The first 3G systems appeared in 1998 with the UMTS (Universal Mobile Telecommunications Service) and CDMA2000 (Coded Division Multiple Access) technologies. Afterward, in 2008, the first 4G systems appeared bringing a set of new technologies, called Long Term Evolution (LTE) due to its extended compatibility for future technologies. Despite the mobile network has more than 7 billions mobile phones in 2015 [7], the market is still growing.

The predictions made by Cisco in [8] forecast an increase in the mobile data traffic by 7x between 2016 and 2021. Additionally, machine-to-machine communications will grow 34% per year in the same period, driven by the Internet of Things (IoT) adoption. Also, the media consumption will increase 9x, accounting as 78% of total mobile traffic in 2021. Furthermore, applications such as real-time video broadcast or tactile internet will require lower levels of network latency and delay. From the operator's perspective, others requirements are made such as flexibility on deployment, and cost reduction to maintain the Total Ownership Cost (TOC) relatively low.

Such requirements from users and operators shapes the target for the upcomming generation of mobile networks. To address all incoming requirements, the radio access network is evolving to use a variety of technologies. For example, Inter-Cell Interference Coordination (ICIC), massive MIMO (multiple-input, multiple-output), and operation of signals in the millimeter wave spectrum. In detail, the ICIC technology provides better signal quality and higher throughput on high interference scenarios. Also, Massive MIMO expands the capacity of the wireless link by the usage of several antennas. Finally, the operation in millimeter waves enables the transmission of higher bandwidth signals and provides more spectrum to be allocated. All these improvements being applied to the network require a great deal of engineering effort.

Due to the distributed characteristic of the existing mobile network, the implementation of interference coordination and spatial diversity between Base Stations are very expensive. In addition, the operation costs of cell-cites are high, mainly due to energy consumption and rent. In this scenario, the idea of a Centralized Radio Access Network (C-RAN) [9] gained attention, where a set of small and cheap remote distributed nodes are connected to a central processing unit. The cost reduction of this architecture can be around 53% in OPEX and 30% in CAPEX as shown in [10]. Furthermore, a centralized signal processing can make easier to implement the coordination and MIMO techniques expected for next generation mobile network.

Although the C-RAN brings several advantages, there are issues to be addressed in order to benefit from the centralization gains. The fronthaul is very important to the centralized RAN, since it connects the network units that capture and process the radio signals. But, the existing fronthaul technologies are very expensive, given that dedicated optical links are used to provide high bandwidth and low jitter. In this scenario, it is necessary to rethink the fronthaul infrastructure in order to reduce costs while still providing a reliable fronthaul transport.

One of the expected features of the next generation fronthaul is the usage of existing low

cost networks, such as Ethernet. This strategy should bring the benefits of statistical multiplexing provided by a packet-network, along with the re-usage of existing infrastructure. Also, the hierarchical structure of Ethernet is advantageous for dense deployment scenarios expected for 5G. In addition, the Ethernet protocols also provide a well known and broadly used set of Operation and Maintenance (OAM) functions. In summary, Ethernet is one of the main technologies in the next generation fronthaul.

This work presents a testbed implementation for Ethernet-Based fronthaul, along with the chalenges and solutions to provide reliable fronthaul transport over Ethernet infrastructure. The fronthaul implementation shown here could be used to test and evaluate a variety of algorithms for fronthaul and C-RAN. For example, this infrastructure was used to evaluate the LTE signal compression of [11] and the transport of compressed IQ signals. In this evaluation, the compressed data is transported over the fronthaul network, decompressed and sent to the air interface through the usage of an external digital-to-analog converter. In addition the analog signal is fed into a signal analyser in order to evaluate the quality metrics of the signal.

#### 1.1 Objectives

Some of the main objectives of this work are:

- To review the basics of existing fronthaul technologies and future trends.

- To present an implementation of fronthaul architecture based on Ethernet.

- To evaluate the impairments of an Ethernet-Based fronthaul into the transported signal.

- To present an implementation of LTE signal compression algorithm in VHDL.

- To evaluate the quality metrics of signal compression over an Ethernet-Based fronthaul.

#### 1.2 Dissertation Outline

Chapter 2 shows an overview of the fronthaul technology, the existing standards, the future trends and current solutions. Initially, a review of the existing fronthaul technologies is shown in Section 2.1. Then, the expected features for the next generation fronthaul are presented

in Section 2.2. Finally, an overview of the signal compression technique implemented in this work is shown in Section 2.3.

Chapter 3 presents the implemented Ethernet-based fronthaul testbed with compression. Initially, the used fronthaul architecture is shown in Section 3.1. After, the VHDL implementation of the compression algorithm is detailed in Section 3.2, along with the developed blocks and its engineering solutions.

Chapter 4 exposes the results collected from the testbed, the evaluated network parameters and the quality aspects of the reconstructed signal after fronthaul transport and decompression.

Chapter 5, contains the final considerations of this work, as long as suggestions future works.

## Chapter 2

## **Fronthaul**

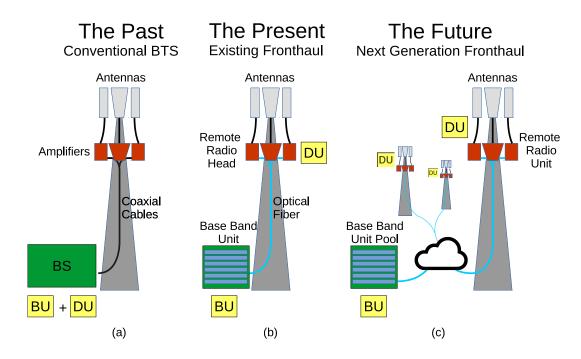

Fronthaul is the name given for the portion of the Radio Access Network (RAN) between digital signal processing and Radio Frequency (RF) signal conditioning. In a high-level view the RAN architecture can be divided in two blocks: The Digital Unit (DU) that modulates the user data into a digital signal according to a specific Radio Access Technology (RAT) and the Radio Unit (RU) which converts the digital signal into analog RF signal. In the existing Base Stations (BS) these two units are connected through a high reliable and fast channel called fronthaul, as show in scenario (b) of Figure 2.1. Over the time the architectural usage of the DU and BU changed as shown in Figure 2.1 and further discussed in this section.

Figure 2.1: The fronthaul evolution.

The split of DU and RU is a well known practice in the telecommunications world. This paradigm is preserved even when both units are physically located at the same space, as shown in Figure 2.1 (a). In this scenario, the concept of fronthaul already existed, but just around 2002 it started to be standardized as a long range digital link. This transformation was motivated by the necessity to increase the mobile coverage and extended the Base Station through Remote Radio Head (RRH), as shown in Figure 2.1 (b). At that time several telecommunication actors started to define new types of interfaces between both units. The efforts pointed in the same direction, a digital interface using optical-fiber medium with high availability and throughput.

Different protocols were defined for the implementation and deployment of fronthaul links, some of the most important ones are: the Common Public Radio Interface (CPRI) [1], developed by group of companies including: Ericsson, Huawei, NEC, Alcatel, Nokia and others. Also, there were the Open Base Station Architecture Initiative (OBSAI) [2], created by another groups of companies including: Samsung, LG, Nokia, Hyunday and ZTE. Additionally, there is a recent effort based on CPRI to provide more interoperability between different RU's and DU's called Open Radio equipment Interface (ORI) [12].

Currently the RAN architecture is going through another round of architectural changes to provide better services at lower costs. These changes are motivated by the high demands for throughput and quality from the consumers, allied with the mobile operators competition for lower costs. In this scenario, the concept of Centralized Radio Access Network (C-RAN) [10] comes up as a solution for cost reduction. As discussed before, this concept proposes to centralize the DU's functions into computing centers, while keep the RU at the coverage areas, as shown in Figure 2.1 (c). This architecture has many advantages such as cost-reduction on deployment and operation, also it is possible to implement interference coordination algorithms easily with centralized processing.

In order to centralize the resources the fronthaul network needs to be redesigned [13] to support the C-RAN at reasonable costs. The existing fronthaul uses point-to-point optical links, which makes the cost of deployment on dense scenario very high. A fronthaul architecture suitable for C-RAN should benefit from the statistical multiplexing provided by packet networks. Also, take in account the network traffic on the network scheduling, providing dynamic flow-control based on the network usage.

Additionally, the network should provide the flexibility for different deployment topologies or even dynamic topology. To provide suitable fronthaul architecture it is possible to ex-

plore the functional split between DU and RU. This means to move some processing from the Base Band Unit to the Remote Radio Head. In this case the RU receives a difference nomenclature, namely Remote Radio Unit (RRU), due to its additional digital processing.

The existing fronthaul transports raw complex samples and uses huge amounts of bandwidth. For example, a single 4G-LTE 20 MHz signal can consume up to 1.2 Gbps, assuming the signal is using 40 bits on each complex sample, which is the maximum defined by CPRI in Section 7 of [1]. These bandwidth requirements are unfeasible for the network densification planned in 5G networks, especially in applications that use, e.g., massive MIMO [14], since the fronthaul bandwidth is proportional to the number of antennas used in the RU.

In this chapter a review of the essential characteristics of existing fronthaul technologies is shown in Section 2.1. Then, the research trends of the Next Generation Fronthaul Interface (NGFI) is presented in Section 2.2. Finally, to support the subsequent chapters a brief introduction to the compression algorithm implemented in this work in shown in Section 2.3.

#### 2.1 Fronthaul Concepts and Existing Technologies

As introduced before, there are three well-defined fronthaul specifications: CPRI, OB-SAI and ORI [15]. Besides having different objectives and procedures, they also have a lot in common when focusing in the fronthaul link itself. For example, both OBSAI and CPRI carry synchronization signals through the fronthaul. Additionally, they all define control and management procedures.

The Common Public Radio Interface (CPRI) specification is an industry cooperation started at 2003 aiming to define a fronthaul link between Radio Equipment (RE) and Radio Equipment Controllers (REC). The CPRI is a essentially simple protocol to transport IQ data, control and synchronization information from the RE to REC. The CPRI is the most widely used fronthaul standard, this specification will be better discussed in Section 2.1.1.

The Open Base Station Architecture Initiative (OBSAI) standard started in 2002 aiming to define a complete architecture for base stations, as will be discussed in Section 2.1.2. The objective of this specification is to standardize the internal blocks of the base station and enable the cell-site to be deployed with equipment from different vendors. The fronthaul as this work defines is actually one of the many interfaces specified by OBSAI standard.

The Open Radio equipment Interface (ORI) standard is relatively recent. It started in 2010

by the Industry Specification Group (ISG). This standard is based on CPRI and aims to specify a more detailed Control and Management Procedure. In CPRI most of these operations are vendor-specific, which makes it difficult of using products from different vendors. Furthermore, the ORI specification defines a compression algorithm to be applied on CPRI signals with large bandwidth [12]. The ORI will be briefly discussed in Section 2.1.3

#### 2.1.1 Common Public Radio Interface (CPRI)

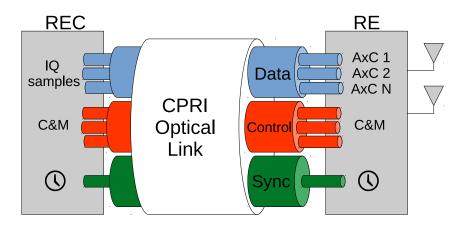

The CPRI specification is the commonly used standard of fronthaul. It defines a communication link between the DU and RU, in fact these entities are called respectively Radio Equipment Controller (REC) and Radio Equipment (RE) in CPRI specification. The link carries not only the complex signal (IQ Data), but also control and clock synchronization information, as shown in Figure 2.2. The CPRI payload can carry several IQ signals, each one encapsulated into an Antenna Carrier (AxC). It can transport different communication protocols, such as GSM, CDMA, LTE or WiMAX. Also, the protocol counts with a set of control information such as Control and Management (C&M) data, protocol extensions and vendor specific information [1].

Figure 2.2: Information carried in CPRI link.

The CPRI link carries frequency and phase synchronization information. Actually this information is provided by the physical layer (PHY). In fact, the optical or electrical interfaces can use Phase Locked Loops (PLLs) to derive a synchronization signal based in the received bit-stream. Such implementation is common in modem applications [16] and is very precise in optical communication due to the low distortion provided by optical media. Also, in CPRI it is possible to measure and compensate the delay on the physical medium, since the topology is very simple. Moreover, the CPRI has control information to indicate the framing synchroniza-

tion. After all the synchronization procedures the CPRI link is capable of achieving a maximum frequency error of 0.002 ppm, and delay accuracy of 16.276 ns [1].

The CPRI specification defines both Optical and Electrical media but it does not describe how the physical layer should be implemented. In fact, the standard just specifies the performance requirements of the PHY such as the Bit Error Rate (BER) under  $10^{-12}$  and the link line-rates, which are listed in Table 2.1. Although the specification defines an electrical interface the existing CPRI deployments for long distances are made with optical medium. The Electrical interface is commonly used in backplane implementations or short distances cooper cabling, under 10 m [1].

**Table 2.1:** CPRI configuration for some of the line rates defined in the specification.

| Option | # of Bytes forming a Word | Bitrate (Mbps) | Line Coding | Line Rate (Gbps) |

|--------|---------------------------|----------------|-------------|------------------|

| 1      | 1                         | 1 x 491.52     | 10/8        | 0.61             |

| 2      | 2                         | 2 x 491.52     | 10/8        | 1.22             |

| 3      | 4                         | 4 x 491.52     | 10/8        | 2.45             |

| 4      | 5                         | 5 x 491.52     | 10/8        | 3.07             |

| 5      | 8                         | 8 x 491.52     | 10/8        | 4.91             |

| 6      | 10                        | 10 x 491.52    | 10/8        | 6.14             |

| 7      | 16                        | 16 x 491.52    | 10/8        | 9.83             |

| 8      | 20                        | 20 x 491.52    | 66/64       | 10.13            |

| 9      | 24                        | 24 x 491.52    | 66/64       | 12.16            |

| 10     | 48                        | 48 x 491.52    | 66/64       | 24.33            |

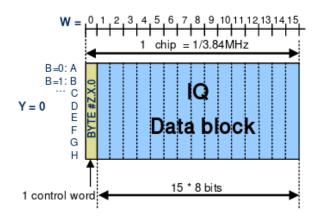

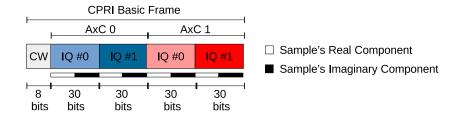

The smallest portion of a CPRI stream is the Basic Frame (BF), it has a unique characteristic, independent of the line rate used the BF has to depart at the fixed rate of 3.84 MHz, this rate is called chip-rate and is a legacy from CDMA applications. In other words, independent of the CPRI line rate, at each 260.41 ns there is a BF departing. The BF is divided internally into 16 words, as shown in Figure 2.3, the bit-width of these words changes with the line-rate option. For example, in the line-rate option 1 the bit-width of each word is 8 bits, while in the line-rate option 2 each word carries 16 bits. Also, the first word of each BF is reserved for CPRI control information, namely the Control Word (CW).

The BF IQ Data block is divided internally into Antenna Carrier Containers (AxC) which

Figure 2.3: CPRI Basic Frame internal structure [1].

form a block of samples from the same antenna as ilustrated in Figure 2.4. The BF can carry several AxC's, organized in ascending order, as long as the link capacity is respected. The number of samples in each AxC container depends on the oversampling ratio with respect to the chip-rate (3.84 MHz). Inside each AxC, the samples are stored in chronological order and consecutively, from LSB to MSB, with interleaved I and Q samples, as shown in the Figure 2.4.

Both Figures 2.3 and 2.4 shows the same CPRI BF setup. They both have a control word of 8 bits followed by a data block of 120 bits, divided in 15 words of 8 bits. Note that the IQ samples of Figure 2.3 does not necessarily use an integer number of words from the data block. In fact, the data block is divided for each antenna carrier and the samples are allocated inside the AxC accordingly to the transported signal.

Figure 2.4: Example of CPRI Basic Frame carrying two signals with 30 bits per IQ sample.

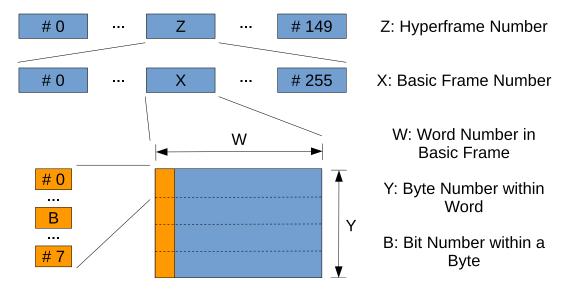

The CPRI BFs are grouped in hyperframes, each one contains 256 BF and takes 66.67  $\mu$ s of transmission time. Additionally, the hyperframe is grouped into a CPRI Frame, containing 150 hyperframes and takes 10 ms of transmission time. There is a nomenclature used to indicate the position of each bit in the CPRI stream. Such convention is represented by a tuple (Z.X.W.Y.B), where Z indicates one of the 150 hyperframes, X indicates one of the 256 Basic

Frames, W indicates one of 16 words within the Basic Frame, Y indicates the byte within a word and B indicates the bit in each byte, as shown in Figure 2.5.

**Figure 2.5:** CPRI naming convention and frame structure [1].

The control words are grouped by hyperframes, each one has 256 Control Words which carries different types of control information. For example, a hyperframe Synchronization word is carried in the first word of each hyperframe. Also, some words are used to allow the communication between the PHY layers of endpoints, called L1 Inband Protocol. In addition, there are words carrying special sequences to help the PHY layer to train is internal PLL's in order to acquire the synchronization. Aside from these fields, there is also space for vendor specific information and others.

The amount of bits to be carried in each BF is dependent on the number of AxC containers  $(N_{AxC})$ , the amount of bits per IQ-sample  $(IQ_b)$  and the sample rate  $(F_s)$  of each AxC signal. As a matter of fact, the CPRI bit-rate  $(R_{CPRI})$  has to be chosen based in the equation:

$$\sum_{i=0}^{N_{\text{AXC}}} IQ_{b,i} \times F_{s,i} \le \frac{15}{16} \times R_{\text{CPRI}},\tag{2.1}$$

where the 15/16 value represents the Control Word overhead. For example, a CPRI stream with two AxC ( $N_{AxC}=2$ ), carrying an LTE 20 MHz signal ( $F_s=30.72\times10^6$ ), with IQ samples represented by 30 bits ( $IQ_b=30$ ), consumes a bit-rate around 1.84 Gbps. Although the closest bit-rate existent, as shown in Table 2.1, is 1.96 Gbps ( $4\times491.52$ ) which is relative to the usage of 4 bytes per word.

Although CPRI is the commonly used protocol, it has a very small protocol defition. On one hand such simplicity makes the standard very flexible and can be applied in different scenarios, on the other it became difficult to assure the interoperability of equipment based only in CPRI specification.

#### 2.1.2 Open Base Station Architecture Initiative (OBSAI)

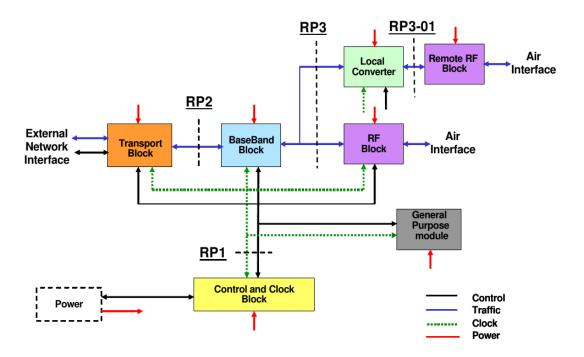

As discussed before, the OBSAI standard defines a whole architecture for the Base Station, including a fronthaul link [2]. The specification defines several basic blocks and interfaces, as shown in Figure 2.6. For example, the *Base Band Block* modulates the information into the IQ signal, while the *RF Block* converts the IQ signal to analog RF. Moreover, the *Control and Clock Block* generates clock synchronization and control information to all the blocks.

Figure 2.6: Overview of OBSAI building blocks [2].

The protocol [17] also specifies the interfaces between the blocks: the Reference Point 1 (RP1) distributes synchronization and control information between the blocks. In addition, the Reference Point 2 (RP2) interfaces the *Base Band Block* with *Transport Block* transporting the user data. Also, there is the Reference Point 3 (RP3) transports the samples between *Base Band* and *RF Blocks*.

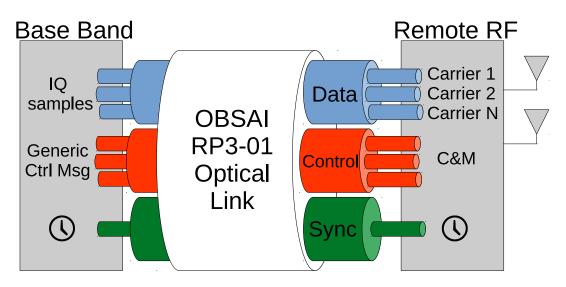

In contrast to the CPRI specification, in OBSAI the IQ data, Control and Synchronization

are provided by three different entities. To extend the range of a divided architecture like this it is necessary a converter to group these information into a single channel. In this scenario, the OBSAI standard defines an extension to the RP3, called RP3-01, to make possible the utilization of Remote Radio Units. On RP3-01 the IQ-Data, Control and Synchronization are carried together into a single long-range link. In this extension the network topology is restricted to chain, ring or tree, just like CPRI. Although the optical link is more commonly used, the RP3-01 also specifies other media such as wireless and cooper cable, as long as the transmission characteristics can met the standard [2].

There are many similarities between OBSAI RP3-01 and CPRI, as shown in Figure 2.7. For example, both are capable to transport the same Radio Access Technologies: GSM/EDGE, CDMA, WCDMA, WIMAX and LTE. Also, both use a reference signal derived from physical layer to provide system-wide clock synchronization. In addition, both standards define optical and electrical interfaces. The former is applied in long-range applications while the latter is used in backplane applications.

Figure 2.7: Information carried by OBSAI RP3 link.

Although the RP3-01 link actually represents the long-rage fronthaul, the characteristics of RP3 are very interesting. For example, IQ traffic is packet-based, so it is possible to use packet switching in hardware to increase efficiency. In addition, the topology of RP3 network is more complex, enabling the usage of mesh or centralized modes. Moreover, the *Base Band Block* could have access to any *RF Block* on the network making possible the cooperation between them.

The OBSAI is a very extensive standard, since it describes the complete architecture of a BS. For example, the C&M procedures for RP3-01 are more complex than the CPRI ones. This reduces the implementation freedom in the fronthaul, but allows the compatibility between equipment. The detailed study of OBSAI specification is out of scope of this work, but it is essential to evaluate the similarities and differences among the available fronthaul techonologies.

#### 2.1.3 Open Radio Equipment Interface (ORI)

The ORI protocol [12] is fully compliant with CPRI specification. In fact it can be seen as an extension to the CPRI specification to provide more interoperability between equipment from different vendors. Among the extensions defined by ORI, the compression of IQ data is an important topic. The standard specifies how the compression should be made and also the allowable degradation such as EVM and latency. Also, in the control and management domain the specification defines software abstractions and configurations not covered by CPRI.

Besides it is possible to compress the stream transported by CPRI, which does not specifies how the signal can be compressed. The ORI, on the other hand, defines a compression technique to be used for the LTE signals with BW higher than 10 MHz. The specified algorithm uses a 3/4 down-sampling and non-linear quantization to remove the redundancy in both frequency and amplitude domains. The protocol also defines how the compressed stream should be mapped in the IQ-data space. Despite the fact that down-sampling provides a 3/4 compression ratio, the final compression ratio is not defined in the specification, since it depends on the statistical characteristics of the signal and the number of bits used in the non-linear quantization [12].

The control and managements features of ORI are much more complete than CPRI. The REC counts with a resource model to store the information of the Radio Equipment (RE). In fact, the REC interfaces with the resource model creating an abstraction layer between the nodes. The resource model provides functionalities to manage the Configuration (CM), State (SM) and Faul (FM) of each RE. With this software abstraction, it is possible to make changes in the RE without directly changing the REC.

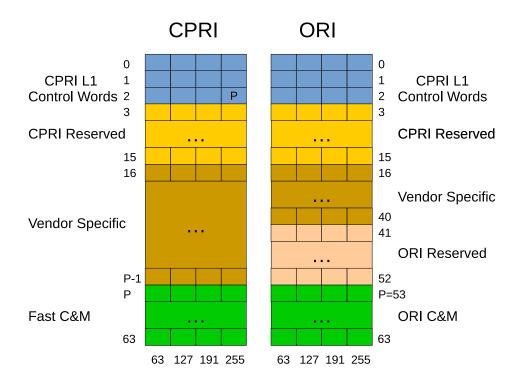

In the CPRI specification, the 256 Control Words are aggregated in groups of four, called control sub-channels. The purpose of each one of the 64 sub-channels is predefined in the CPRI specification, as show in Figure 2.8. The ORI specification respects CPRI, but the vendor-

specific and Fast C&M sub-channels are remapped to allocate ORI data. The vendor-specific area is reduced and gives place to an ORI reserved area, as shown in Figure 2.8. Also, the CPRI's Ethernet data-link protocol defined in Fast C&M became a full TCP/IP stack protocol in ORI C&M. The usage of a full stack makes possible to use other well-known protocols in the ORI link. For example, it is possible to use DHCP for IP address distribution and FTP for configuration file transfer.

Figure 2.8: CPRI and ORI control sub-channels mapping.

As seen in Figure 2.8, the vendor specific fields are not removed from ORI, but they use a reduced space. In CPRI the vendor specific area had a configurable amount of words from 15 to 192. However, in ORI these fields uses 100 words while the rest of the Control Words are divided between ORI Reserved fields and ORI C&M link, the former uses 48 words while the latter uses 44 words.

#### 2.2 Next Generation Fronthaul Interface (NGFI)

The existing fronthaul technologies meet the needs of the last generation RAN architecture. Although for the 5th generation of mobile communications, it is still necessary some effort to adapt or re-create the technologies to meet the requirements of capacity and cost. The main

objective of the fronthaul in the next generation is to enable the radio access network centralization and reduce the costs of network deployment. Of course, the centralization itself can bring several benefits such as resource re-utilization, virtualization and better spectrum usage.

The traffic demand shaped the evolution of physical layer modulation and coding techniques. As a result, the single-link capacity is very close to the Shannon's limit. On the other hand, the usage of multi-antenna techniques multiplied the overall link capacity, which generates the necessity of Base Stations with even more antennas. In addition, the signal interference once seen as a problem to be fought, now can be used constructively to increase the signal strength. In this scenario, the fronthaul has to connect several coordinated Radio Units to the central BS processing.

As shown previously, the existing fronthaul distributes the IQ samples, control and synchronization information, thus the NGFIs should be capable to transport the same information with lower costs. Between the difficulties to produce such network is the prohibitive amount of bandwidth used in the existing fronthaul. As already discussed, an LTE signal can consume it to 1.2 Gbps from the fronthaul. Obviously such bit-rate values can be decreased by reducing the number of bits used to represent each sample, but this will deteriorate the signal quality.

Moreover, the usage of dedicated optical links to transport the fronthaul information increases the overall cost of the network. Although the Wavelength-Division Multiplex (WDM) technology can be applied to aggregate several optical channels into a single optical fiber, the equipment cost is still high. On the other hand, the widely used Ethernet equipment provides a low-cost industry standard solution. In addition, the usage of packet-based statistical multiplexing promises gains to the network efficiency. Also, Ethernet is very simple to deploy and scale, which makes the Ethernet transport a desired solution for NGFI. In addition the Ethernet protocols already have a complete set of OAM functions for troubleshooting and management

In the following sections a set of characteristics desired for the NGFI will be highlighted. For example, the benefits and difficulties to use a packet-based fronthaul transport is shown in Section 2.2.1. Distinct functional splits are discussed in Section 2.2.2 which are used to lower the fronthaul transmission rate by move some functions from BBU to RRU. And finally, Section 2.3 shows how signal compression can reduce the bit rate requirement of the fronthaul.

#### 2.2.1 Packet-Based Fronthaul

As discussed before, the existing fronthaul uses dedicated optical links due to the strict requirements of the fronthaul specification. However, this deployment is inefficient from the perspective of network utilization. For example, at night when the network usage decreases, the fronthaul link has to be active to provide the coverage, even if there is no user to be covered. Due to its static configuration, the existing fronthaul can not benefit from the tidal wave effect of network usage, which is the cyclic variation of the network load over the day.

On the other hand, packet-based networks such as Ethernet are very efficient to accommodate on network usage changes, due to the packet switching methodology. As said before [18], both industry and operators agree that the NGFI should be packet-based. In fact, this paradigm change would bring more flexibility to the fronthaul, although it is necessary to evaluate the challenges generated by the packet network.

There are two ways to think the adaptation of the fronthaul to packet-based network. The first consists to evolve the Ethernet infrastructure to provide the fronthaul requirements. Another is to change the base station architecture to take in account the packet-based impairments. There are several groups discussing which techniques should be used and the optimal solution, such as the IEEE-1914 [19] and IEEE-1904.3 [20].

Of course, the existing Ethernet infrastructure is not reliable: the best-effort characteristic forces the higher layer protocols to have extra procedures to assure the information transport. On the other hand, there is work being done in the IEEE Time-Senstive Network (TSN) task force to assure the quality of service for streams being transported over the Ethernet. The aforementioned task force specifies some techniques to assure the Ethernet quality such as: Scheduled Traffic [21], Frame Preemption [22] and Link Reservation [23].

The Ethernet standard is evolving to provide transport with less Packet Delay Variation (PDV) and Round Trip Time (RTT) while maintaining the high throughput. On the other hand, fronthaul requirements are very tight. A transport network to provide such parameters will eventually not be cost effective. In this scenario, the fronthaul has to introduce techniques to overcome the Ethernet impairments, and provide the fronthaul transport even on imperfect Ethernet network.

The packet delay variations can be reduced using buffers to store samples before forwarding to the next node. In fact, this technique reduces the PDV by introducing delay, relative to buffering time. Such technique can be applied as soon as the delay budget is met. Also, the

RTT requirements for fronthaul can be relaxed by rethinking the time budget over the communication stack. Since on centralized architecture the upper layers of the stack will use less time to communicate inside a Radio Computing Center.

In addition, the signal compression techniques shall evolve to provide more signal quality in bandwidth limited scenarios. Also, the evolution of transport protocols of fronthaul over Ethernet should provide more robustness to the network impairments, such as packet drop and network congestion. In this scenario, a desirable feature is the adaptation of the compression ratio to the network load state.

Although the centralization shall facilitate the implementation of MIMO and interference mitigation/coordination techniques, these applications require frequency, phase and time synchronization between the network nodes. In such circumstances, it is possible to use the Precision Time Protocol (PTP) [24] to provide the required synchronization. The PTP is a network protocol defined by IEEE-1588 and used in packet-based networks to provide clock synchronization.

Aside from PTP it is possible to use different synchronization sources over Ethernet fronthaul. For example, the Global Navigation Satellite Systems (GNSS) which is an effective solution to synchronize outdoor nodes. Moreover, it is possible to distribute synchronization through the physical layer as implemented in the ITU G.8262 specification, called SyncE [25]. This solution requires an special implementation of the Ethernet physical layer, since the Ethernet is intrinsically asynchronous.

The discussed impairments and solutions does not require the Radio Access Technology to be upgraded. On the other hand, by adaptations to the RAT it is possible to achieve better results in the centralization over a packet-based fronthaul. This scenario will be discussed in the next Section.

## 2.2.2 Functional Split between BBU and RRU

Beyond the search to provide a highly reliable packet-based fronthaul network, there are also other ways to provide the fronthaul service based on existing Ethernet infrastructure. For example, it is possible to rethink the split of functionalities between the BBU and RRU. In other words, offload some BBU functionalities to the RRU. This strategy can relax the requirements from the fronthaul while still maintain some centralization gain. There is a clear trade-off between centralization gain and fronthaul requirements [26].

There are different scenarios for functional split, for example the scenario implemented by CPRI and OBSAI is the full-centralization, shown in Figure 2.9 as (a). In this scenario, the RRU just contains the analog converters and RF conditioning circuitry, in other words all the signal processing and upper layers are executed in the BBU. As a result, this scenario demands high throughtput and low latency from the fronthaul. For example, in CPRI the maximum RTT is 5  $\mu$ s, while the bandwidth for an LTE signal 20 MHz with 2x2 MIMO can be up to 1.8 Gbps, as shown in Table 2.2.

**Figure 2.9:** LTE base station possible functional splits: (a) All process centralized in the BBU, (b) The OFDM modulation is executed in RRU, (c) The resource mapping and modulation is executed in RRU, (d) The whole PHY layer is executed in RRU, (e) All functions except the PDCP is executed in the RRU.

**Table 2.2:** Fronthaul requirements of different functional split from [3].

| Scenario | BW*                        | RTT                | Latency              |

|----------|----------------------------|--------------------|----------------------|

| (a)      | 1.8 Gbps                   | $5~\mu \mathrm{s}$ | $150~\mu \mathrm{s}$ |

| (b)      | 590 Mbps                   | 1 ms               | $150~\mu \mathrm{s}$ |

| (c)      | 86 - 530 Mbps <sup>1</sup> | 3 ms               | $150~\mu \mathrm{s}$ |

| (d)      | 70 Mbps <sup>1</sup>       | 3 ms               | 2 ms                 |

| (e)      | 70 Mbps <sup>1</sup>       | 100 ms             | 5 ms                 |

<sup>\*</sup> Based on an LTE 20 MHz 2x2 MIMO signal

<sup>&</sup>lt;sup>1</sup> Depends on LTE Network Load

The full-centralization scenario can provide complete centralization gains. On the other hand, the fronthaul necessary to accomplish this objective has very high requirements, which increase the overall cost of the fronthaul network. Not only the necessary bandwidth is very high but also the RTT delay and latency are very low, which requires a big effort to encapsulate this type of network on the existing Ethernet infrastructure.

Other functional splits are also possible, for example to offload the OFDM processing into the RRU, as represented in scenario (b) of Figure 2.9. In this scenario, just the frequency domain IQ samples are transported over the fronthaul, while the OFDM processing including the Cyclic Prefix insertion are executed in the RRU. This type of split can reduce the fronthaul bandwidth up to 30%, as shown in [3]. Also, the RTT delays are relaxed due to the LTE framing structure. On the other hand it is still attached to the LTE slot boundaries.

The Lower PHY scenario reduces the bandwidth requirements from the fronthaul, and is still capable to centralize the MIMO precoding operations. In addition, the interference coordination technique can also be applied in the frequency domain before the OFDM modulation. On the other hand, this scenario still demands very tight latency requirements, which makes difficult the usage of several hops in a Ethernet network.

Another important split is the scenario (c) in Figure 2.9, called Upper PHY. In this scenario, the resource mapping and all the modulation is made in the RRU. This method actually benefits from the eventual low usage of the LTE signal, since the unused Resource Blocks (RB) will not be transported over the fronthaul. In this scenario, the network tidal wave effect could be used to reduce the required bandwidth on low network usage.

Although the Upper PHY method provides lower bandwidth requirements, the centralization gains is also lower. Since in this method the MIMO precoding is moved to the RRU, it is more difficult to implement spatial multiplexing techniques. In addition, the latency requirements are still very tight due to the channel information validity. In fact, all the PHY based split functionalities suffer from the same effect, since the maximum allowed latency has to be within the channel information valid period.

In addition to the previous split methods, it is possible to use the well-defined interface between MAC and PHY as another functional split, as shown in the scenario (d) of Figure 2.9. Different from the previous scenarios this one has relaxed latency and RTT requirements. In fact these values are just bounded to the HARQ maximum response delay. Also, in this method the bandwidth utilization is essentially composed by the user's traffic.

Although for the fronthaul such relaxed parameters would represent a cost reduction, the gains with centralization would be low, given that most of the processing would be made in the RRU. But, In this scenario, it still possible to achieve some gain by the application of Coordinated Scheduling [27, 28]. In such method, the transmission of each node in the network is scheduled in order to reduce the overall interference.

The last functional split reviewed here, is the scenario (e) of Figure 2.9, which is actually very similar to the distributed architecture currently available. Such method centralizes the higher layers of the base station such as RRC and PDCP. In this scenario, the bandwidth usage on the fronthaul is slightly lower than the previously shown scenario (d). On the other hand, the RTT and latency are relaxed since there is no boundaries from the HARQ operations.

The low requirements of scenario (e) makes this functional split desirable, even if the centralization gains from coordination and interference mitigation are nonexistent. In fact, this scenario is already provided by products such as the Ericsson solution for C-RAN [29].

As discussed, each functional split can provide different requirements for the fronthaul and respectively distinct centralization gain. The possibility to relax the requirements on Ethernet-based fronthaul is very interesting to be applied on the scenarios where the Ethernet network is congested. With the different functional splits, a centralized controller can be able to chose the optimal scenario depending on the network state.

#### 2.2.2.1 Antenna Independent Traffic

To satisfy the predicted increase in the network usage, hundreds of antennas are planned to be used on the Radio Access Technology. In this scenario, it is very desirable to transport a single stream independent of the number of antennas and separate this stream in the RRU. This is actually a trade-off with the centralized processing expected for interference coordination and mitigation. From one side it is useful to centralize the process, but with massive amount of antennas, the fronthaul will have problems to transport these signals.

In this scenario, the tradeoff has to be evaluated on each case. For example, on beamforming applications it is interesting to decentralize the beam-form algorithm, since it can be applied in the time-domain samples at the PHY lower levels. On the other hand, the operations of coordination and spacial diversity would benefit more from the centralized method, since the coordination information is more easily collected.

#### 2.2.2.2 BBU and RRU dynamic mapping

Another important topic is the mapping between BBU and RRU, that means which BBU will process the signals of each RRU. In the existing network this mapping is static and realized at the network configuration, but the fronthaul can enable a more flexible mapping. For example, on high traffic demands the network can choose to share the processing between different BBU pools. In this scenario, the fronthaul has to follow a defined mapping between RRUs and BBUs.

In addition, there is a cost reduction attached to a flexible mapping, since in the low usage scenarios the network could centralize the processing and turn-off the unused resources. In fact, this dynamic topology changes can benefit even more from the tidal wave effect in the network usage.

## 2.3 Fronthaul's Signal Compression

The bit-rate is a critical resource for the NGFI mainly due to the high requirements defined in the existing fronthaul network. As seen in the previous sections, it is possible to reduce these requirements by the usage of different functional split between BBU and RRU. On the other hand, this technique also changes the achieved centralization gains. Another possibility to reduce the bandwidth requirements while still providing the centralization gain is to compress the signal transported over fronthaul.

This section discusses the algorithm used as basis for the compression implementation made in this work.

## 2.3.1 PUSQH Compression Algorithm

The compression implementation made in this work uses the algorithm Predictive Uniform Scalar Quantization with Huffman (PUSQH), described in [11] and developed at UFPA. This algorithm compresses the LTE signals to be transported over the fronthaul. It is a combination of OFDM adapted Linear Predictive Coding (LPC) and Huffman coding. This section will give a high-level view of the algorithm while the deep theoretical investigation can be found in [11].

To easily understand the algorithm application, let us follow the operation of compression. The PUSQH method encodes the real (I) and imaginary (Q) samples independently. The first

step is to remove the cyclic prefix of the OFDM signal creating the signal x[n], where  $0 \le n < N-1$  and N is the number of samples per OFDM symbol. The first P samples of each OFDM symbol are used to initialize the predictor filter in both, the encoder and decoder, as proposed in [11]. The remaining samples of x[n] are encoded with LPC and Huffman.

In PUSQH the compression is applied on each time-domain OFDM symbol. The first step to be made in order to compress the signal is to remove the Cyclic Prefix, as show in Figure 2.10. Then, a Linear Predictive Coding (LPC) is applied to the signal and derives an error reference that represents the difference between the original signal and the predicted one. Finally, the error signal is compressed with Huffman code in order to further reduce the amount of bits transported.

Figure 2.10: PUSQH compression flow graph.

The difference between the original signal and predicted signal, called prediction error, has a lower variance than the original signal. Thus, LPC enables to compress the prediction error with lower bits than the original signal and achieve the same level of distortion.

Based in the linear prediction theory [30] it is possible to estimate a system that predicts the behavior of a given signal, based on its characteristics. For example, the Levinson-Durbin algorithm uses the auto-correlation information of a signal to derive a FIR filter that can predict the next samples under certain error, based on a linear combination of the previous samples.

As a matter of fact, the PUSQH usage of prediction and quantization is also known as Differential Pulse-Coded Modulation (DPCM). It is a compression algorithm based in closed-loop predictive quantization. Such strategy is commonly used in the compression of audio and video and was shown by [11] that it can be also customized for LTE signals.

The P initial samples of each OFDM symbol are used to initialize the predictor filter, so these samples are losslessy encoded and transmitted to the decoder. This operation resets the prediction filter at the beginning of each OFDM symbol and is very important to keep the error within an acceptable range, as shown in [11]. Also, this imposition will drive some key project decisions in the hardware implementation.

After the application of the predictive quantization, the PUSQH algorithm also applies a

Huffman coding to the quantized error, in order to reduce the necessary amount of bits to be transported, without further distortion. This technique also benefits from the statistical characteristics of the error signal, since the probability distribution of the quantized error is approximately Gaussian.

One of the main advantages of the PUSQH algorithm is the low usage of computational resources. Even though the training stage of the prediction filter can use some computational resource, this stage can be performed off-line. As a matter of fact, the application of the prediction filter has very low cost, since the filter order is normally low. This makes the usage of PUSQH algorithm affordable even on scenarios with scarce resources.

# Chapter 3

# **Fronthaul Ethernet Compression Testbed**

As discussed in the previous sections, the usage of common Ethernet links to carry fronthaul streams could bring more flexibility and lower cost to the Next Generation Fronthaul Interface. In this context, the compression of fronthaul traffic is an enabling technology that reduces the huge requirements of the fronthaul transmission rate.

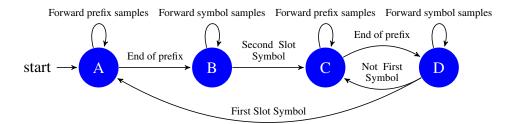

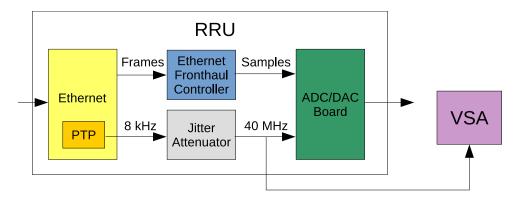

Similarly to the existing fronthaul technologies shown in Section 2.1, the hardware setup presented here consists of a BBU and RRU. The BBU reads LTE signals from its memory and sends over the network through the implemented fronthaul infrastructure. On the other end, the RRU receives Ethernet frames containing fronthaul data and recovers the transported LTE signal. At last the LTE signal reconstructed in the RRU is sent to an analog front-end to be analyzed in the real-world by external equipment.

The presented fronthaul testbed is implemented mainly in VHDL. Other resources were used such as IP-Cores and C code. In detail, the IP-Cores have been used for common hardware blocks such as the interfaces with Ethernet, Memory, and ADC/DAC interfaces. Also, the C language was used in software drivers to initialize and control the testbed. Moreover, MATLAB plays an important role to generate and validate the parameters used to configure the VHDL implementation.

The code is tested in real-time on a experimentation setup consists of two Virtex 7 FPGA boards and one Ethernet switch as shown in Figure 3.1. The process made on each board is shown in Figure 3.2 and described in subsequent sections. This setup makes possible to test the algorithm into real conditions. In addition, the signal transported over the fronthaul is reconstructed by the FPGA board represented by RRU and converted to analog to be analysed externally.

Figure 3.1: Hardware setup of the testbed FPGA boards.

This work presents an architecture to test and evaluate strategies and algorithms for next generation fronthaul that uses Ethernet as infrastructure, as detailed in Section 3.1. Furthermore, the work uses the architecture to implement a compression algorithm for LTE signals, as described in Section 3.2.

## 3.1 Ethernet Fronthaul Testbed

The fronthaul architecture presented in this work aims to map a CPRI stream into Ethernet frames. In other words, the CPRI data is generated and mapped into Ethernet frames. As shown in Figure 3.2, the proposed architecture employs two pairs of blocks: one to generate and consume CPRI streams and other to convert them into Ethernet Frames. Additionally to the CPRI traffic, there is also clock synchronization packets traveling over the Ethernet link provided by the IEEE-1588 protocol.

Figure 3.2: Fronthaul testbed architecture.

The blocks are designed to be reused on both Downstream (from BBU to RRU) and Upstream (from RRU to BBU) since the operation executed by each block is the same on both scenarios. On the other hand, the block configured for BBU operation have different input and output than in RRU. For example, the **CPRI Source** block at BBU receives samples from memory while the same block in RRU receives samples from the analog front-end.

The synchronization procedures defined on IEEE-1588 protocol, and further discussed in Section 3.1.3, use a special implementation strategy. In fact, these operations are hardware-assisted, which means that most of the protocol is implemented in software except the procedures that need strict timing. For example, the protocol messages are generated in software but fields with departure and arrival times are populated in hardware.